FLIP-FLOP adalah unsur memori yang menyimpan digit memori dalam bentuk voltase rendah atau tinggi.Flip-flop merupakan rangkaian yang terdiri dari dua elemen aktif yang kerjanya saling bergantian. Flip-flop ini tidak mempunyai tabel kebenaran yang pasti. Flip-flop bersifat bistable (dua kondisi yang stabil 0 atau 1).kondisi ini tidak akan berubah jika tidak ada input yang masuk.

Fungsinya : - menyimpan bilangan biner

- mencacah pulsa

- menyerempakkan rangkaian aritmatika

Jenis-jenis flipflop diantaranya :

1. RS flip-flop

2. JK flip-flop

3. D flip-flop

4. Master-Slave flip-flop

1. RS Flip-flop

RS Flip-flop yaitu rangkaian flip-flop yang mempunyai 2 jalan keluar Q dan Q’. Simbol-simbol yang ada pada jalan keluar selalu berlawanan satu dengan yang lain. RS flip-flop adalah flip-flop dasar yang memiliki 2 masukan yaitu R (reset) dan S (set). Bila S diberi logika 1 dan R diberi logika 0,maka output Q akan berada pada logika 0 dan Q’ pada logika 1. bila R diberi logika 1 dan S diberi logika 0 maka keadaan output akan berubah menjadi Q berada pada logik 1 dan Q’ pada logika 0.

Gambar lambang RS flipflop

RS flip-flop merupakan dasar untuk menyusun berbagai jenis flip-flop yang lainnya. flip-flop RS dapat disusun dari dua gerbang NAND atau dua gerbang NOR

Gambar RS flip-flop dari gerbang NAND

Skema rangkaian gambar diatas

Tabel kebenaran RS flip-flop

Gambar Rs flip-flop dari gerbang NOR

Skema rangkaian gambar diatas

Tabel kebenaran RS flip-flop

Penjelasan gambar diatas bahwa kita dapat membuat keluaran Q=1 dengan mengeset flip-flop dan membuat keluaran Q=0 dengan mereset flip-flop dari kondisi stabil. Pada rangkaian flip-flop terdapat gerbang NAND, mengeset dapat dilakukan dengan memberi nilai S=0 dan mereset dapat dilakukan dengan memberi nilai R=0, pada rangkaian gerbang NOR mengeset dapat dilakukan dengan memberi nilai S=1 dan mereset dapat dilakukan dengan memberi nilai R=1.

RS Flipflop dengan clock

Flip-flop ini merupakan pengembangan dari RS flip-flop dengan menambahkan dua gerbang NAND pada RS flip-flop gerbang NAND dan gerbang AND pada RS flip-flop gerbang NOR.hal tersebut bertujuan untuk masukan pemicu disebut dengan sinyal clock untuk mengubah nilai yang ada.

Gambar lambang RS flip-flop dengan clock

Gambar rangkaian RS flipflop dengan clock pada gerbang NAND

Skema Rangkaian gambar diatas

Tabel kebenaran RS flipflop dengan clock pada gerbang NAND

Gambar rangkaian RS flipflop dengan clock pada gerbang NOR

Skema rangkaian gambar diatas

Tabel kebenaran RS flipflop dengan clock pada gerbang NOR

Dilihat dari hasil table kebenarannya terlihat bahwa untuk sinyal clock yang tinggi, flip-flop ini bekerja seperti RS flip-flop, untuk sinyal clock yang rendah, keluaran Q tidak tergantung kepeda input R dan S, tetapi tetap mempertahankan keadaan akhir sampai datang sinyal clock yang berikutnya.

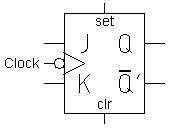

2. JK Flip-flop

JK flip-flop adalah modifikasi dari RS flip-flop. Sebuah JK flip-flop dibentuk dari RS flip-flop dengan tambahan gerbang AND pada sisi input RSnya. Ketika kita sampai pada rangkaian yang mencacah maka JK flip-flop adalah unsure memori yang ideal untuk digunakan.

Lambang a,Lambang b,Lambang c

Gambar a lambang JK flip-flop dari rancangan apapun,J dan K rendah tidak menghasilkan apa-apa. Gambar b lambang baku untuk JK flip-flop dengan fungsi tambahan ini.perhatikan bahwa ia bersulut tepi positif serta memerlukan set untuk preset dan clr untuk clear.Gambar c merupakan JK flip-flop lainya yang terdapat secara komersial, flip-flop ini bersulut tepi negative.ia memerlukan set rendah untuk preset dan clr rendah untuk clear.

Gambar contoh rangkaian JK flip-flop

Gambar diatas menunjukan satu cara untuk membuat JK flip-flop.J dan K adalah masukan kendali karena mereka menentukan apa yang dilakukan flip-flop ketika tepi kunci waktu positif tiba.karena gerbang AND itulah rangkaian itu bersulut tepi positif.

Tabel kebenaran JK flip-flop

Ketika J dan K rendah kedua gerbang AND menjadi disabel. Karena itu, pulsa kunci waktu tidak mengakibatkan apa-apa. Ketika J dan K keduanya 0, maka Q mempertahankan nilai akhirnya.

Ketika J rendah dan K tinggi gerbang diatas menjadi disabel sehingga tidak ada jalan untuk menset flip-flop. Satu-satunya kemungkinan adalah mereset. Ketika Q tinggi, tepi kunci-waktu positif berikutnya tiba,lalu gerbang bawah meneruskan sulutan riset. Ini memaksa Q untuk menjadi rendah. Karena itu, J=0 dan K=1 menunjukan baha tepi kunci waktu positif berikutnya mereset flip-flop(terkecuali Q memang sudah rendah).

Ketika J tinggi dan K rendah, maka gerbang bawah menjadi disabel, sehingga tidak mungkin untuk mereset flip-flop. Namun dapat menset flip-flop.ketika Q rendah maka Q’ tinggi, karena itu pada tepi kunci-waktu positif berikutnya.ini menggerakkan Q ke status tinggi.J=1 dan K=0 menyebabkan tepi kunci waktu positif berikutnya menset flip-flop.(kecuali Q memang sudah tinggi).

Ketika J dan K tinggi,maka flip-flop dapat diset atau direset, jika Q tinggi maka tepi kunci waktu berikutnya, gerbang bawah meneruskan sulutan reset. Ketika Q rendah tepi kunci waktu positif berikutnya, gerbang atas meneruskan sulutan. Karena itu J=1 dan K=1 menyebabkan flip-flop togel(mensakelar ke status lawannya) pada tepi kunci waktu positif berikutnya.

3. D Flipflop

D flip-flop adalah rangkaian yang hanya memerlukan satu masukan data dan dua keluaran.

Gambar lambang D flip-flop

Ingatlah selama clock rendah, flip-flop tergrendel pada keadaan terakhirnya.ketika clock tinggi, flip-flop menset atau mereset, tergantung pada nilai D.

Gambar D flip-flop

Gambar diatas adalah cara membuat D flip-flop.data D menggerakkan masukan S serta pelengkap D menggerakan masukan R. karena itu, D’ tinggi menset flipflop.serta D rendah meresetnya. Ia akan mereset atau menset, D menjadi tinggi atau rendah.flip-flop seperti ini tidak pernah digunakan orang.

Gambar D flipflop dngn clock

Clock rendah membuat gerbang AND disabel sehingga mencegah flip-flop untuk berubah keadaan. Dengan kata lain, waktu clock rendah flip-flop tergrendel pada keadaan terakhirnya.

Ketika clock tinggi, nilai D menjadi penting, D tinggi menset flip-flop.sedangkan D rendah meresetnya.

Tabel kebenaran D flip-flop

Meringkas operasi tsb. X menyatakan 0 atau 1 sehingga, selama clock rendah, nilai D adalah tidak penting, karena flip-flop tetap tergrendel. Ketika clock tinggi maka Q=D.

4. Master slave

Gambar rangkaian Master Slave JK Flip-flop

Sebuah Master Slave JK Flip-flop dibentuk dari 2 buah RS flipflop, dimana operasi dari kedua RS flip-flop dilakukan secara bergantian dengan memberikan input yang berlawanan pada kedua RS flip-flop. Prinsip dasarnya jika clock diberi input 1 gerbang AND 1 dan 2 akan aktif, Master akan menerima data yang dimasukan melalui input J dan K sementara gerbang AND 3 dan 4 tidak aktif, hasil outputnya=0, sehingga Slave tidak ada respon(kondisi tidak berubah). Dan jika clock diberi output 0, gerbang 3 dan 4 aktif, Slave akan mengeluarkan output di Q dan Q’, master tidak merespon input, karena gerbang AND 1 dan 2 tidak aktif.

3 komentar:

wah thanks berat ya...

tertolong nih buat ngerjain tugas fisika bikin laporan yang susah....

oke..sama-sama

apa tidak apa2 kalo clk nya g di pasang ke gate AND? clknya trus ker SR aja?.... thx b4.....

Posting Komentar